April 1953

HEWLETT

#### table of contents

April 1997, Volume 48, Issue 2

# **Articles**

A Family of Instruments for Testing Mixed-Signal Circuits and Systems by Robert A. Witte

**Testing a Mixed-Signal Design Based on a Single-Chip Microcontroller** *by Jerald B. Murphy*

**Design of a Mixed-Signal Oscilloscope** by Matthew S. Holcomb, Stuart O. Hall, Warren S. Tustin, Patrick J. Burkart, and Steven D. Roach

**Sustained Sample Rate in Digital Oscilloscopes** by Steven B. Warntjes

Acquisition Clock Dithering in a Digital Oscilloscope by Derek E. Toeppen

An Oscilloscope-Like Logic Timing Analyzer by Steven B. Warntjes

High-Sample-Rate Multiprocessor-Based Oscilloscopes by R. Scott Brunton

A Dielectric Spectrometer for Liquid Using the Electromagnetic Induction Method by Hideki Wakamatsu

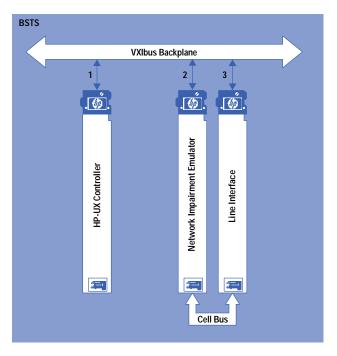

# Emulating ATM Network Impairments in the Laboratory

by Robert W. Dmitroca, Susan G. Gibson, Trevor R. Hill, Luisa Mola Morales, and Chong Tean Ong

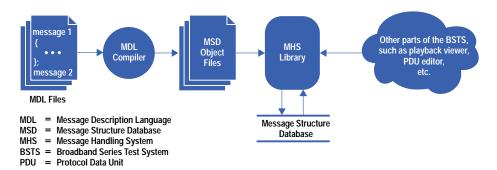

A Message Handling System for B-ISDN User-Network Interface Signaling Test Software by Satoshi Naganawa and Richard Z. Zuo

# Object-Oriented Network Management Development

by Peter E. Mellquist and Thomas Murray

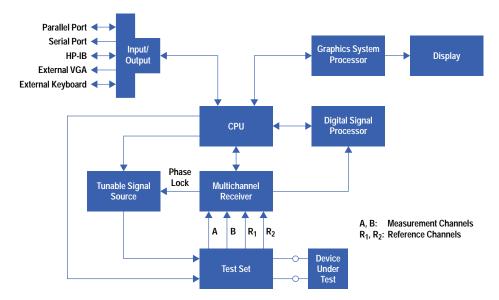

# Design of an Enhanced Vector Network Analyzer

by Frank K. David, Frederic W. Woodhull II, Richard R. Barg, Joel P. Dunsmore, Douglas C. Bender, Barry A. Brown, and Stanley E. Jaffe

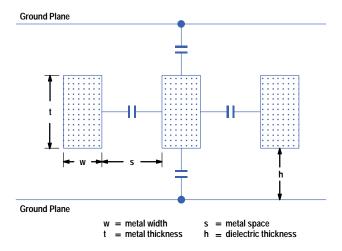

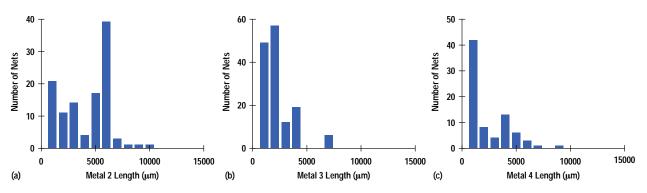

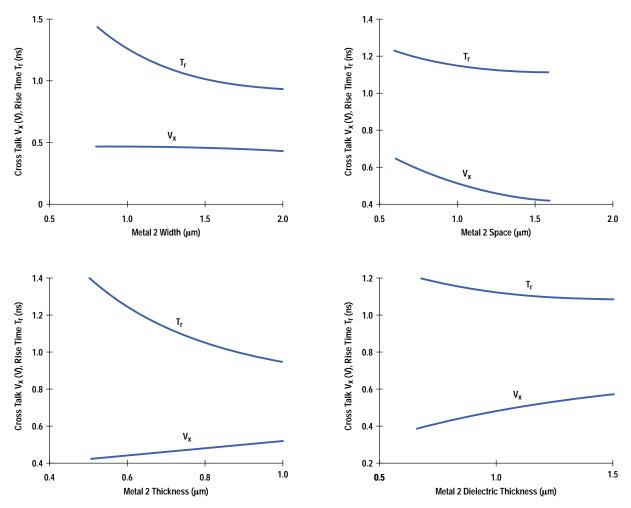

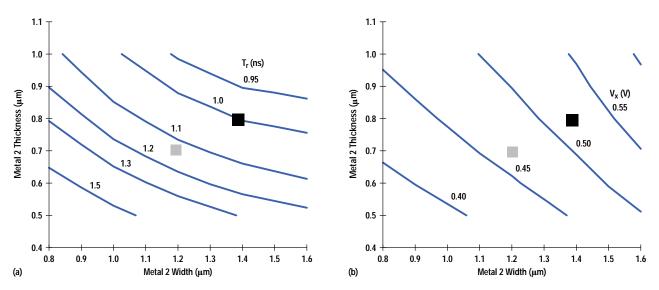

**Optimization of Interconnect Geometry for High-Performance Microprocessors** *by Khalid Rahmat and Soo-Young Oh*

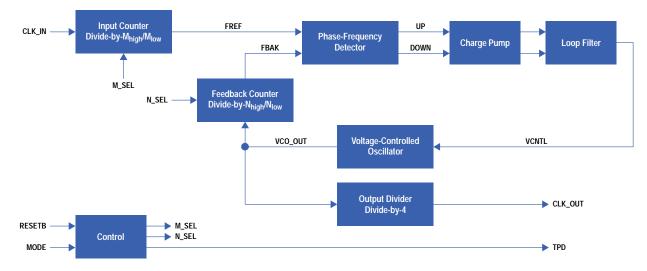

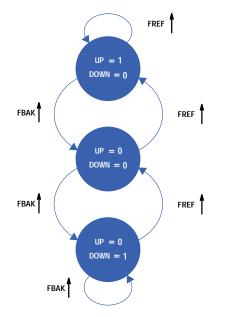

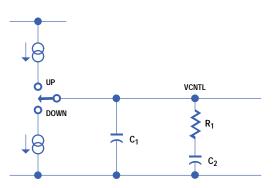

**Designing, Simulating, and Testing an Analog Phase-Locked Loop in a Digital Environment** by Thomas J. Thatcher, Michael M. Oshima, and Cindy Botelho

Analog Behavioral Modeling and Mixed-Mode Simulation with SABER and Verilog

by Ben B. Sheng, Hugh S.C. Wallace, and James S. Ignowski

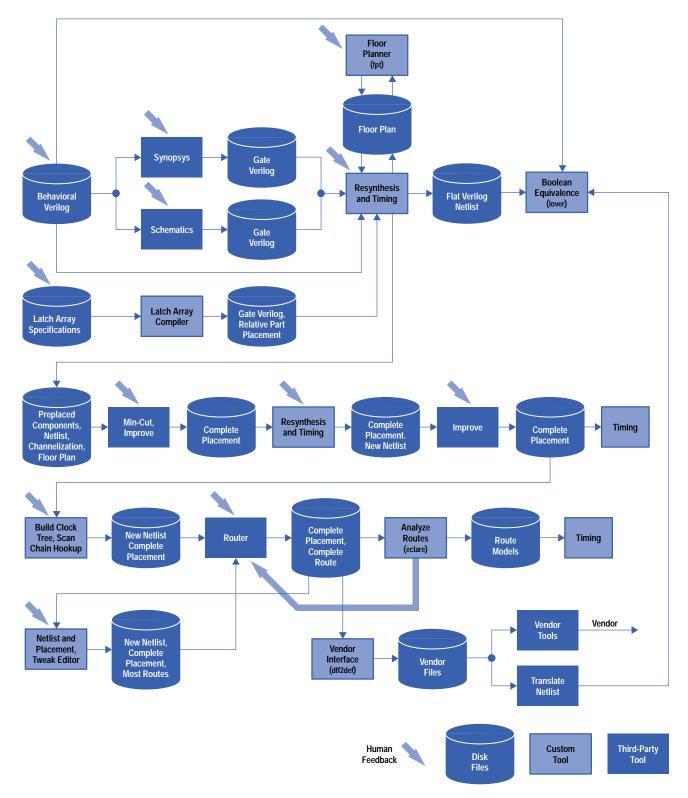

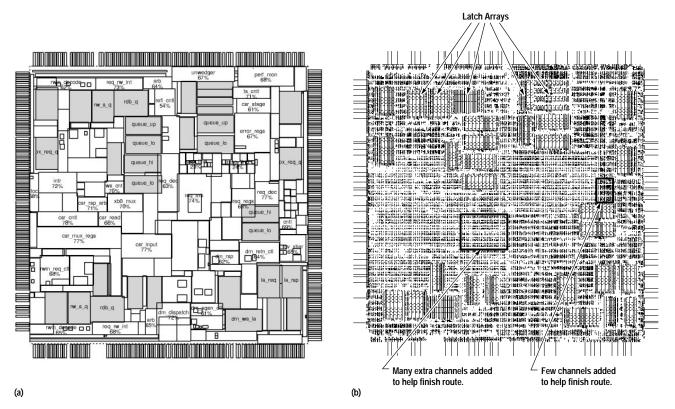

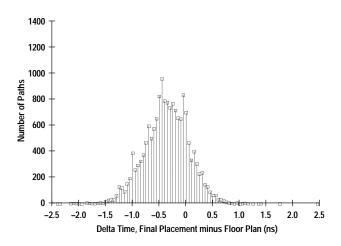

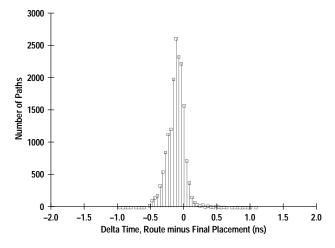

# Physical Design of 0.35- m Gate Arrays for Symmetric Multiprocessing Servers

Fast Turnaround of a Structured Custom IC Design Using Advanced Design Tools and Methodology

by Rory L. Fisher, Stephen R. Herbener, John R. Morgan, and John R. Pessetto

# **A Family of Instruments for Testing Mixed-Signal Circuits and Systems**

This entirely new product category combines elements of oscilloscopes and logic analyzers, but unlike previous combination products, these are "oscilloscope first" and logic analysis is the add-on.

# by Robert A. Witte

Electronic circuits have been a part of modern life for so long that most people take them for granted. Some devices are inherently electronic in nature such as telephones, radio receivers, calculators, and personal computers. Other devices started out as mostly mechanical and have gradually had more electronics incorporated into them over time. Electronics has made its way into automobiles, cameras, water heaters, home appliances, elevators, thermometers and weighing scales. This "electronics everywhere" trend has gradually filled modern life so that it is difficult to imagine what life would be like without all those electrons running around doing their jobs.

Most early electronic systems were analog, especially if they interfaced to real-world physical phenomena. The emergence of digital technology resulted in the gradual diffusion of digital gates into applications that were once exclusively analog. Thus, an "analog moving to digital" trend emerged as the number of digital gates per acre of silicon continued to grow at a fast rate. Analog circuits will never be totally replaced, since for the most part the real world stubbornly retains its analog behavior and circuits that interface to this world must retain at least some analog circuitry. The result is that many electronic systems are mixtures of analog and digital circuitry that have come to be known as "mixed analog and digital" or simply "mixed-signal."

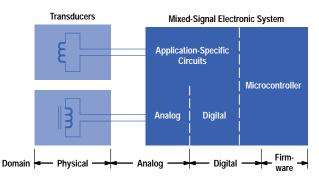

The single-chip microcontroller has emerged as an important component in these mixed-signal designs. Of course, microcontrollers have been around for decades, doing the lowly control tasks in cost-sensitive applications while their more powerful siblings ("real" microprocessors such as an Intel80486 or a Pentium<sup>®</sup>) got all of the attention, usually because of their critical role in personal computers. Meanwhile, the single-chip microcontroller improved in performance, moving from 4 bits to 8 bits and 16 bits while also improving in cost-effectiveness. Without much fanfare, these single-chip devices found their way into a wide range of designs, causing one author to refer to them as "The Ultimate ASIC."<sup>1</sup> These devices are often used to control or measure a physical system (e.g., antilock braking, camera control, appliance controls, industrial control systems). A generic block diagram for such a system is shown in Fig. 1, and an example of a mixed-signal single-chip microcontroller is presented *Subarticle 1a*.

This increased use of mixed-signal electronics is showing up in a wide variety of industries and applications. Consumer electronics is an obvious area, with mixed-signal designs being used in CD players, stereo receivers, tape decks, and camera electronics. Similarly, communications devices such as modems, telephone answering machines, and multimedia boards for PCs all use mixed-signal electronics. There are many applications in industrial electronics, including process control, industrial water heater controls and other sensor-based systems. The growing area of mechatronics (the merger of mechanical and electronics, including subsystems such as the previously mentioned antilock braking systems and ignition control. Biomedical applications are another emerging area, with mixed-signal electronics being applied in pacemakers, hearing aids, and other medical devices.

Fig. 1. Block diagram of a generic mixed-signal system.

Systems can be totally digital if only on-off control is required. More likely, there is some physical quantity being measured or controlled that requires a portion of the electronic system to be analog. The increased use of sensors allows engineers to create smarter control systems that monitor physical events and do a better job of controlling the system. A good example of this is antilock braking systems in automobiles. In this case, electronics (including sensor technology) is being used to make the braking effectiveness of the automobile far better than would be possible in a purely mechanical system.

#### Oscilloscopes

For designers of mixed-signal systems, the troubleshooting tool of choice is the oscilloscope. The versatility of the oscilloscope for viewing a wide variety of waveforms allows the design engineer to see what's happening in the device under test. Other test instruments may also be used but the oscilloscope remains the first tool that most users turn to for debugging circuits.

Mixed-signal engineers expect many things from their oscilloscopes. The oscilloscope must have sufficient fundamental performance in terms of bandwidth and sample rate to capture and display signals accurately and reliably. At the same time, the oscilloscope must be easy to use so that the engineer can focus on the operation of the circuit and not on the operation of the oscilloscope. In the heat of the troubleshooting battle, it is very distracting for the user to have to interrupt the debug process to deal with an uncooperative test instrument.

With the increasing digital content in these mixed-signal systems, a two-channel or even a four-channel oscilloscope quickly runs out of inputs. It is just not possible to view the complete operation of even a simple digital circuit with a conventional oscilloscope. Take the trivial example of a 4-bit up/down counter. With four output lines, a clock input, a load input, and an up/down count control, the counter will have at least seven digital signals associated with it (and perhaps more). Since an engineer cannot view all of these signals at once with an oscilloscope, the usual remedy is to apply "mental storage." The engineer applies the oscilloscope probe to a particular signal, views it, and stores the image into mental memory, then moves to other signals of interest and repeats the process. Eventually, a picture of the entire circuit's operation is formed in the mind of the debug artist. Sometimes this picture is precise and meaningful but sometimes it is cloudy and full of uncertainty.

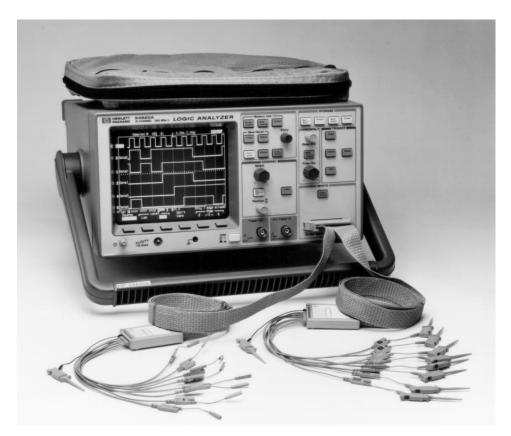

# Logic Analyzers

The idea behind a logic analyzer is that many digital signals can be viewed simultaneously so that an engineer can obtain a complete and accurate picture of what is really going on in a circuit. One of the trade-offs made in a logic analyzer is that only digital signals can be viewed and only an idealized reconstruction of the waveform is possible. That is, the waveform is treated as a purely binary signal and is displayed as either a logic high or a logic low, with no detail of the actual waveform shape. This is a reasonable compromise since the major problem in a digital system is determining whether the circuit operation is correct. It is a functional check that does not require the waveform detail. In fact, it can be argued that complete waveform detail is mostly visual noise when checking the functionality of a digital circuit.

As logic analyzers evolved, they tended to be optimized for solving the really tough problems that come with complex, bus-based microprocessor systems. Most modern logic analyzers have a minimum of 32 channels and may have 128 channels or more. They also provide extensive trigger and selective storage features that make them unmatched in debugging and troubleshooting power. This power inherently leads to a certain level of complexity in the analyzer; complexity that can be a barrier to the oscilloscope-oriented engineer. Many designers of mixed-signal systems, even when limited by the number of channels on their oscilloscopes, remain reluctant to adopt logic analyzers.

#### **Mixed-Signal Oscilloscopes**

Further investigation into this avoidance of logic analyzers revealed the opportunity for a new kind of test instrument that would expand the channel count of the oscilloscope without losing its inherent appeal. A series of market research activities were launched to determine how to fill this gap between oscilloscope and logic analyzer. Clearly, engineers were limited by the number of channels on their oscilloscopes but they were not always adopting a logic analyzer as the solution. What eventually emerged is an entirely new product category that combines elements of oscilloscopes and logic analyzers.

As a world leader in logic analyzer products, HP had already pioneered the creation of hybrid instruments that combine oscilloscope and logic analyzer technology (HP 1660 Series and HP 16500 Series logic analyzers, for example).<sup>2</sup> However, these products were designed with full-featured logic analysis as their top priority and the oscilloscope capability is an adjunct to the analyzer. The new product line starts with the oscilloscope user in mind. These products are "oscilloscope first" and logic analysis is the add-on.

A family of HP products aimed at mixed-signal testing has been created. The HP 54600 product line now offers the following set of test instruments appropriate for mixed-signal work:

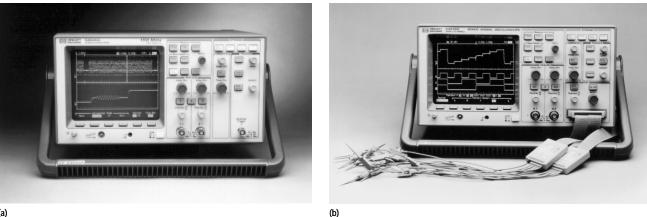

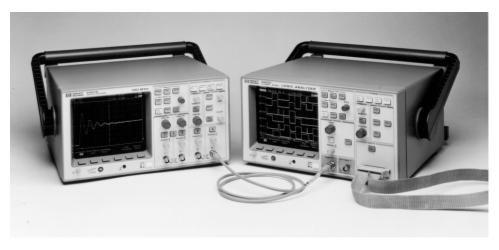

• The HP 54645D mixed-signal oscilloscope (Fig. 2) combines two 100-MHz oscilloscope channels with 16 logic timing channels. This is the ultimate mixed-signal testing tool because it seamlessly integrates oscilloscope channels and logic timing channels. This product includes HP's MegaZoom technology, which delivers the benefits of a million-sample memory for each channel without the agonizingly slow responsiveness normally associated with deep memory.

(a)

Fig. 2. The HP 54645A two-channel oscilloscope (a) and the HP 54645D mixed-signal oscilloscope (b), both with MegaZoom, are examples of the new product category of mixed-signal oscilloscopes.

- The HP 54645A two-channel oscilloscope with MegaZoom (Fig. 2), a general-purpose oscilloscope, is the first affordable 100-MHz digital oscilloscope with sufficient sample rate and memory depth to capture a wide range of analog and digital signals. The HP 54645A has the same basic MegaZoom technology as the D version but does not have the logic channels.

- The HP 54620A/C 16-channel logic timing analyzer is an easy-to-use logic analyzer designed to be the perfect companion product to an oscilloscope, perhaps the one that the user already owns. This logic analyzer has an oscilloscope user interface metaphor so that it is familiar and easy-to-use for the typical oscilloscope user.

- The HP 54615B and 54616B/C 500-MHz two-channel oscilloscopes are general-purpose oscilloscopes that provide the bandwidth and sample rate (1 GSa/s and 2 GSa/s, respectively) needed for high-speed digital work while maintaining the responsiveness and trustworthiness required for mixed-signal debugging and troubleshooting. The HP 54616C has a flat-panel color display.

While each of these products represents a particular mix of features and performance, they all share the core values of the HP 54600 product line:

- Direct Access Controls on Main Functions. The volts/division, time/division, position, and trigger level controls are all dedicated knobs for easy access.

- Responsive User Interface. Instant response to front-panel changes is critical to making an oscilloscope easy to use. All of these products provide sufficient processing power to maintain a responsive front panel.

- Fast Update Rate and Low Dead Time. These products use multiprocessor architectures to make sure the display is updated quickly.

- Digital Peak Detection. These products have true digital peak detection, which is available on all sweep speeds. Digital peak detection keeps the sample rate operating at its maximum specification even on very slow time base settings, guaranteeing that short-duration events (such as glitches) are not missed (see Article 4). Peak detection also prevents aliasing. On the HP 54620A/C logic analyzers, the equivalent feature is glitch detection.

- HP Proprietary Alias-Reduction Techniques. All of the HP 54600 Series oscilloscopes employ HP's proprietary alias-reduction techniques to reduce the possibility of an erroneous displayed waveform (see Article 5).

- Compact and Portable. These products pack a lot of measurement power into a compact size and the small footprint helps save precious bench space.

- Optional HP-IB, RS-232, and Parallel Interfaces. These products offer a choice of computer and printer interfaces.

- Optional Measurement/Storage Module. This option provides FFT, advanced math, and pass/fail mask testing (oscilloscope products only).

The accompanying articles in this issue describe some of the key design contributions incorporated in these products.

#### References

- 1. "Single-Chip Microcontrollers: The Ultimate ASIC," *Electronic Engineering Times*, March 20, 1995.

- 2. 1996 HP Test and Measurement Catalog, Hewlett-Packard Company.

Pentium is a U.S. registered trademark of Intel Corporation. Intel80486 is a U.S. trademark of Intel Corporation.

# **Mixed-Signal Microcontroller**

As explained in the accompanying article, HP's new family of mixed-signal test instruments is designed to meet the needs of designers of products that are partly analog and partly digital, such as antilock braking systems, camera control systems, appliance controls, and industrial control systems. Many of these products are based on single-chip microcontrollers. The producers of these products are demanding simpler and cheaper electronic assemblies from system developers, and this pressure to reduce costs is fed back to microcontroller suppliers in a number of ways, most of which can be summarized as a greater integration of mixed-signal peripherals with the microcontroller core. Thus, the microcontrollers themselves are becoming mixed-signal devices.

For example, Microchip Corporation's PIC14000 microcontroller integrates a number of peripherals that are often requested by system designers. This peripheral set, which is well-suited for slow-moving real-world analog signals, is packaged with Microchip's 14-bit microcontroller core to create the PIC14000. The peripherals are:

- Single-slope analog-to-digital converter (ADC)

- 16-bit programmable timer with capture register

- 16-ms maximum conversion time at maximum resolution with 4-MHz clock

- 4-bit programmable current source

- 8 external channels, two with selectable level-shift inputs

- 6 internal channels

- On-chip temperature sensor

- Two comparators with programmable references

- Internal bandgap voltage reference

- Voltage regulator control output

- On-chip low-voltage detector.

Wes Reid Senior Applications Engineer Standard Microcontroller & ASSP Division Microchip Corporation

# Testing a Mixed-Signal Design Based on a Single-Chip Microcontroller

The HP 54645D mixed-signal oscilloscope simplifies the testing and debugging of microcontroller-based mixed-signal designs with its integrated analog and digital channels.

# by Jerald B. Murphy

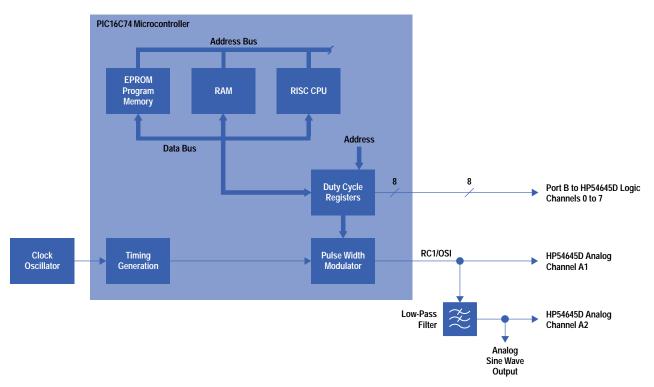

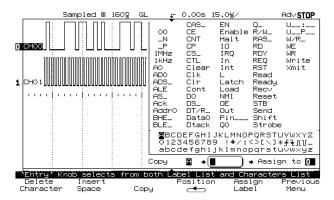

This article presents an example that shows how the HP 54645D mixed-signal oscilloscope (see *Article 1*) might be applied to understand the operation of a device that produces a 60-Hz reference signal that is used by other devices in a system. The reference sine wave is produced by low-pass filtering a pulse width modulated signal generated by a PIC16C74 8-bit CMOS single-chip microcontroller (see block diagram, Fig. 1). This is a fairly typical application of these powerful, low-cost devices. The low cost and availability of single-chip microcontrollers has resulted in their application in areas that previously were nonelectronic, and in some cases even mechanical. Examples include the replacement of clockwork-driven appliance switches and motor control.

*Fig. 1.* Block diagram of the PIC16C74 microcontroller and low-pass filter implementing a reference sine wave generator, showing the hookup to the HP 54645D mixed-signal oscilloscope.

In this application we have a very stable signal being produced with a simple design. An analog design with the same level of performance would have been much more complex.

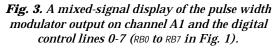

The pulse width modulator (PWM) of the PIC16C74 microcontroller is controlled by an 8-bit input. This input is provided by a lookup table stored in the microcontroller's memory. In operation the microcontroller sends the first control input to the PWM from the lookup table, waits a specified time, and then sends the next value in the lookup table to the PWM. When the last value in the lookup table is sent to the PWM, the microcontroller's counter is reset to start the process again at the top of the table. The input to the pulse width modulator is available on the microcontroller's port B RB0-RB7 data lines.

In this application we can view the PWM's output and the 8-bit data that produced that output. This will enable us to verify the correct operation of the PWM.

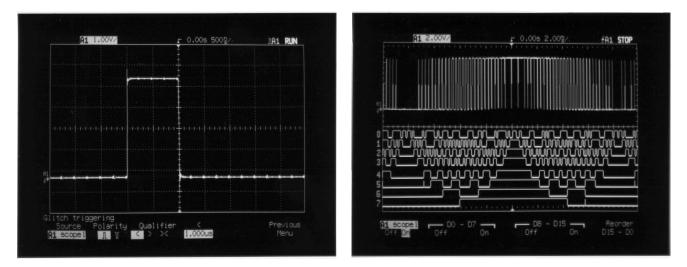

The first step in testing this design is to verify the operation of the PWM. We want to make sure that the minimum pulse width is correct and the maximum pulse width is less than a period of the system's basic timing. The minimum pulse width is found by using the HP 54645D's glitch triggering mode. We simply use one of the analog channels to probe the PWM and then select the "less than" mode of the glitch trigger to find the minimum pulse width.

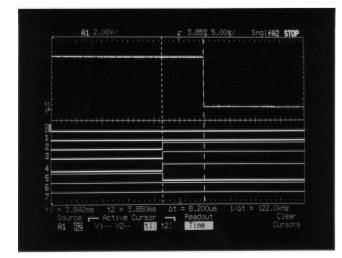

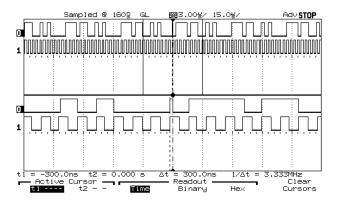

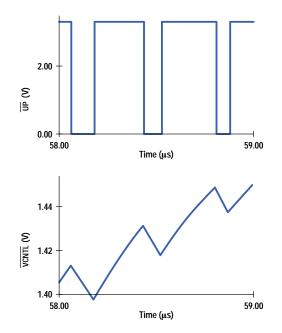

The minimum pulse width should be approximately 1  $\mu$ s, so we set that as the search condition in the glitch trigger. Now, decreasing this value until the mixed-signal oscilloscope stops triggering (which happens immediately) isolates the minimum pulse width (Fig. 2). Applying the mixed-signal oscilloscope's automatic measurement feature gives a measurement of this pulse width as 1.02  $\mu$ s. The maximum pulse width can be located in the oscilloscope's deep memory by delaying the sweep by 8.3 ms (half the period of the 60-Hz signal). Here we observe a pulse that is 256  $\mu$ s wide with clean transitions on either side. By probing the microcontroller's port B data lines we can observe the input and output of the PWM. The deep memory of the mixed-signal oscilloscope greatly simplifies the task of observing this operation. Simply pressing the Autoscale key results in a display that contains both the analog channel displaying the PWM output and the eight logic channels displaying the PWM's input. The resulting display is not well triggered but the waveform data needed to observe the PWM operation is captured in the oscilloscope's deep memory. Simply pressing the Run/Stop key freezes the display (Fig. 3) so that the contents of the oscilloscope's deep memory can be examined by panning and zooming, using the oscilloscope's time base controls.We see that the minimum and maximum values of the pulse width are related to the 00 and FF values of the digital inputs. The display is zoomed in on a leading edge of one of the PWM pulses and the delay from the digital input to the PWM output is measured to be 8.2  $\mu$ s (Fig. 4). We can conclude that the PWM is operating properly.

Fig. 2. Glitch triggering is used to locate the minimum pulse width of the pulse width modulator of the PIC16C74 microcontroller.

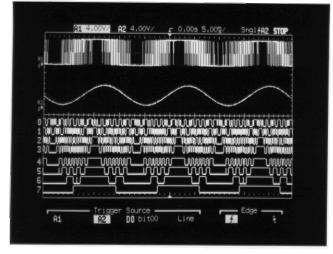

The next set of questions relate to the low-pass filter. One question might be, "What is the delay from the digital input of the PWM to the output of the low pass filter?" This measurement is easily accomplished with the HP mixed-signal oscilloscope. Connect a second oscilloscope probe to the output of the filter and press Autoscale. The resulting mixed-signal display contains the digital input to the PWM, the variable-width pulse output of the PWM, and the output of the low-pass filter. The oscilloscope is now triggered on the rising edge of the sine wave output of the low-pass filter. The total operation of the system under test is now displayed on one screen (Fig. 5).

The delay from the digital input of the PWM to the output of the low-pass filter can be measured by first placing a cursor on a known value of the digital input lines. After selecting the hexadecimal cursor readout mode, the t1 cursor can be placed at the point where the digital lines first reach the value of FF (Fig. 6). The t2 cursor is then placed at the maximum value of the sine wave. Switching the cursor readout to time, this delay is measured to be 2.610 ms (Fig. 7). This measurement was made without having to take into consideration any additional delays that might be associated with the instrumentation. The deep memory of this product allows this measurement to be made on data that was gathered on one trigger. There was no need to be concerned about errors that might be produced by having the display made up of many cycles of system operation.

In this example we have seen how the HP 54645D mixed-signal oscilloscope simplifies the testing and debugging of microcontroller-based mixed-signal designs with its integrated analog and digital channels. The user of the HP mixed-signal oscilloscope has the advantage of MegaZoom technology's high-speed display, instantly responding controls, and deep memory to simplify the testing phase of the project. The integrated analog and digital channels produce an easy-to-understand view of the device under test. The glitch triggering was used to isolate a point of interest. In this example there was little need to use any of the mixed-signal oscilloscope's pattern or advanced pattern triggering capabilities. These

Fig. 4. A mixed-signal measurement. The delay from digital control to pulse width output is measured to be  $8.2 \,\mu s$ .

**Fig. 5.** A view of the total operation of this mixed-signal system. The pulse width modulator output is channel A1, the output of the low-pass filter is channel A2, and digital channels 0-7 are the pulse width modulator control lines.

*Fig. 6.* Cursor t1 is placed at the point where the digital control lines enter the state FF.

Fig. 7. With cursor t2 placed on the peak of the low-pass filter output and the cursor readout changed to time, the delay from digital command to output is measured to be 2.610 ms.

features provide even more debugging power when needed. Both cursor and automatic measurements were used to characterize the device under test.

# Acknowledgments

Thanks to Art White, applications consultant for Western Regional Marketing, for developing this application based on the PICDEM-2 model DI163002 demonstration board. The PIC16C741 and PICDEM-2 are products of Microchip Technologies, Inc. 2355 West Chandler Blvd., Chandler, Arizona 85224-6166 USA. Western Regional Marketing, Inc. of Westminster, Colorado is the distributor for Microchip products serving the geographic area where the author is located. Special thanks to Mary Kerr, a former HP employee and now a consultant, for leading the effort to develop this application for Hewlett-Packard. Johnnie Hancock managed the relationship with Microchip. Additional help was received from Steve Warntjes and Bob Witte.

# **Design of a Mixed-Signal Oscilloscope**

This combination of a digital oscilloscope and a logic timing analyzer provides powerful cross-domain triggering capabilities for capturing signals in mixed-signal environments. MegaZoom technology, consisting of advanced acquisition techniques and dedicated signal processing, maintains display responsiveness while making optimal use of deep sample memory.

# by Matthew S. Holcomb, Stuart O. Hall, Warren S. Tustin, Patrick J. Burkart, and Steven D. Roach

The design of the HP 54645A/D oscilloscopes introduced in *Article 1* began with the HP 54645A, envisioned as a performance upgrade to the HP 54600 Series oscilloscopes.<sup>1</sup> These oscilloscopes, introduced in 1991, have an almost analog look and feel. Their three-processor design yields unprecedented display update rate and responsiveness at an affordable price. The major design goal for the HP 54645A was to improve the sample rate performance by an order of magnitude while maintaining the responsiveness and display update rate of the existing HP 54600 Series products.

Ultimately, two new products were created: the HP 54645A two-channel oscilloscope and the HP 54645D mixed-signal oscilloscope. The mixed-signal oscilloscope is a new product category that adds 16 logic timing analyzer inputs to the two channels of oscilloscope input. In addition to displaying all 16 logic channels, the HP 54645D provides advanced logic triggering functions on patterns that can span all 18 channels.

The HP 54645A and 54645D were designed concurrently. We made every effort to have the oscilloscope-only product (the HP54645A) be simply the combination product (the HP54645D), with an external trigger circuit substituted for the digital channel subsystem. Even the firmware ROM in the two products is identical.

#### Architecture

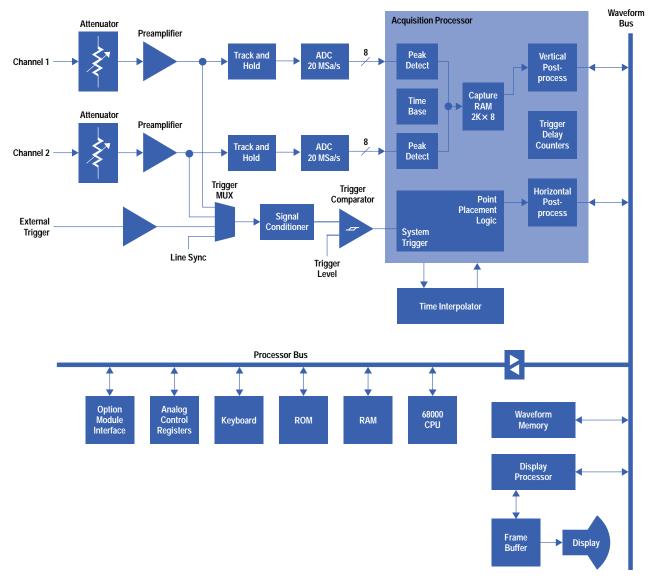

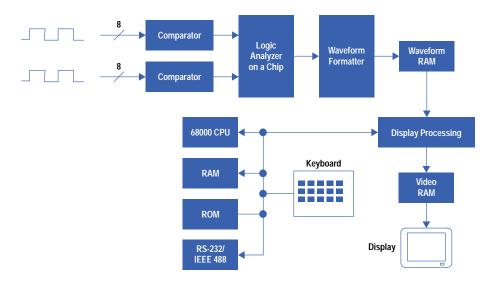

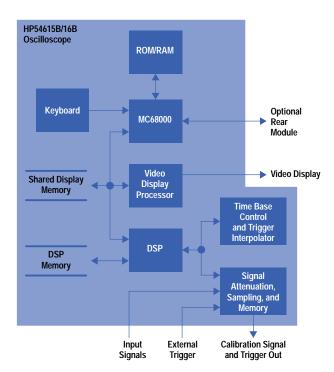

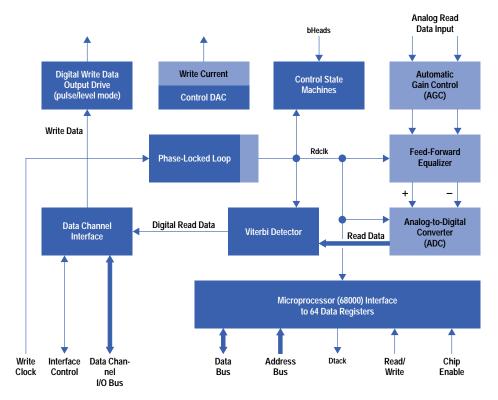

We started the design by modifying the architecture. A simplified block diagram of an HP 54600 Series oscilloscope is shown in Fig. 1. Two ICs form the core of the system: the acquisition processor and the display processor. The display system was left alone and only the acquisition circuitry was redesigned. We kept the same display, the same package, the same analog front end, and the same host 68000 processor.

In the original HP 54600 design, the acquisition processor IC was responsible for taking the digitized samples from the analog-to-digital converter (ADC) and placing them into an external memory as time-ordered pairs, which the display processor IC placed on the CRT display. More specifically, the acquisition tasks include:

- Generation of the sample clocks for the ADCs and controlling the decimation of the sample clock and dither algorithms for use at slower time base settings.

- Peak detection of the ADC data. This block calculates the minimum and maximum values of the sampled data.

- Intermediate storage of the ADC data (or minimum/maximum pairs if the peak-detector is used) into an internal circular 2K-sample memory. This memory, known as the *capture RAM*, holds the data until the trigger point is calculated.

- Accepting the analog trigger from one of the channels and measuring the time between the trigger and one of the sample clock edges.

- After the trigger is found, unloading the data from the capture RAM into an external RAM known as the *waveform RAM*. For each sample value, a corresponding x-axis (time) value is calculated.

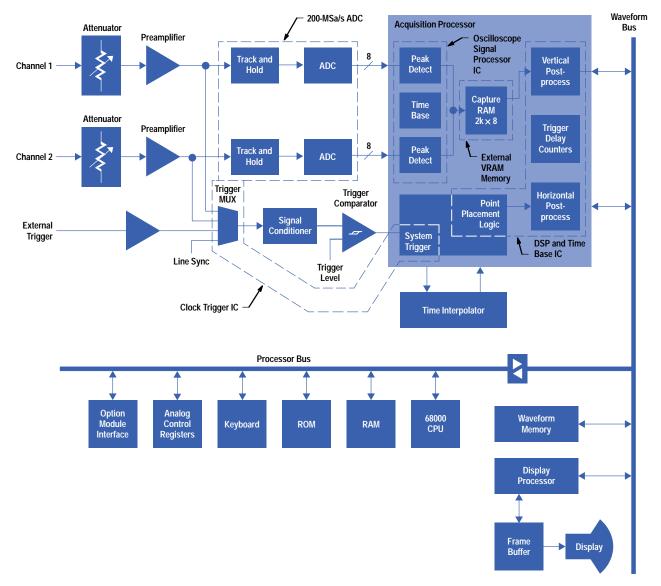

All of these tasks were integrated into one chip for the HP 54600 oscilloscopes. For the new products, we divided the above functions into separate, discrete components, as shown in Fig. 2.

**Clock Generation**. Much of the difficulty of the original one-IC design stemmed from unwanted coupling between the sample clocks and the trigger clocks. In a digital oscilloscope, such coupling can severely corrupt the time base fidelity, causing time-axis nonlinearities ("bowing in time"), time-axis discontinuities, and sample bunching. In a higher-frequency instrument, the design of the clocking and trigger systems would have been all the more difficult. Consequently, the new products have a separate, dedicated bipolar IC for handling the clock generation and triggering.

Peak Detection. As before, we needed a handful of digital circuitry that stands between the ADC and the intermediate capture memory. This circuitry takes the 200-MSa/s 8-bit ADC data, calculates the appropriate minimum and maximum values, and stores the results sequentially into memory.

Fig. 1. Original HP 54600 Series oscilloscope block diagram.

Additionally, we decided to improve the averaging performance by digitally low-pass filtering the incoming sampled data before storing it into memory. This technique (later named *smoothing*) requires summing 32-bit values at a 200-MHz rate.

We chose to realize these functions in a CMOS gate array known as the *oscilloscope signal processor IC*. In addition to the functions described above, this IC decelerates (or fans out) the ADC data, steering and decimating the sampled data into the capture memory as described next.

**Capture Memory.** Recall that this memory is used to hold the incoming data until a suitable trigger point has been found and measured. In the HP 54600, the acquisition processor, being a fully custom design, had an internal 2K-byte (16K-bit) memory. Such memories are less available in gate array technology, so combining this function with the oscilloscope signal processor IC wasn't a particularly attractive option.

At 200-MHz rates, or 400-MHz rates for the timing channels, high-speed memories aren't off-the-shelf plug-in items. A traditional ECL design would be power hungry and costly. Our solution was to use commercially available video memories (VRAMs). Since these parts have a 50-MHz 16-bit interface, we could store data at a 100-Mbyte/s rate per memory. Each channel then requires only two devices. Since these memories are dual-ported, we can access the data (for plotting) simultaneously with the acquisition process, an advantage that we capitalized on further, as explained later.

Each VRAM has a capacity of 4M bits, resulting an 8M-bit (or 1M-byte) memory depth per channel. This increased memory depth is a huge improvement over previous designs and delivers value to the customer through increased time capture at a given sample rate (see *Article 4*).

Time Base and VRAM Controller. Along with the advantages of all of this deep memory came the problems of deep memory. Another CMOS gate array IC was designed for managing the storage and retrieval of data into the VRAM array. Its primary

*Fig. 2.* HP 54645A oscilloscope architecture compared to the HP 54600. The topology remains relatively unchanged. Only the logic partitioning is different.

job is to provide the necessary commands to the VRAM to manage the data flowing into and out of its two ports. It also provides a high-speed interface to this memory for the rest of the system at a sustained reading or writing rate of over 10 million bytes per second. It controls the main time base algorithms, the trigger delay and holdoff counters, and a variety of interacquisition and intra-acquisition sample dithering circuits.

**Data Processing.** In previous products all of the time-axis acquisition algorithms were hard-coded into hardware. Such a system was fast and inexpensive, but more difficult to change. Therefore, for the new oscilloscopes, instead of hard-coding the mathematics into the time base and VRAM controller IC, we opted to use an off-the-shelf digital signal processor, or DSP: Texas Instruments' 25-MHz TMS320C50.

Like its predecessor, the DSP's job is to use the trigger information to determine where each of the samples stored in the VRAMs should be placed on the screen. Additionally, it handles all of the pan-and-zoom operations, allowing the user to redisplay the acquired data at other time base or delay settings after the acquisition is complete.

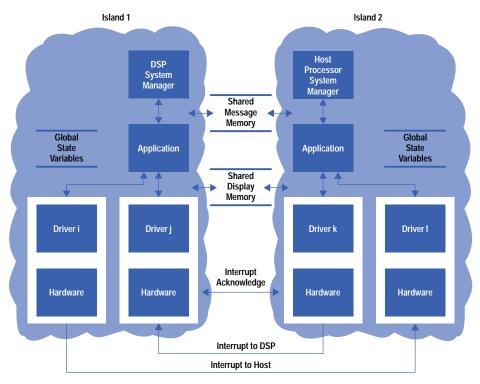

# Mixed-Signal Oscilloscope

The idea behind the HP 54645D mixed-signal oscilloscope is to provide a truly seamless analog and digital waveform viewing instrument. A key goal for the project was to provide a product that was greater than the sum of just the two instruments. By combining an oscilloscope and a timing analyzer, we hoped to provide functionality and ease of use never before available in a laboratory quality oscilloscope.

Careful attention was paid to knitting together the analog and digital halves of the mixed-signal oscilloscope. Anything you can do with the analog channels, you can do with the digital channels: viewing, automatic measurements, triggering, and so on. Both halves share the same time base and the triggering system can operate on all 18 channels.

Where the oscilloscope channels have a *oscilloscope signal processor* CMOS gate array to decelerate and postprocess the ADC data, the digital channels have a similar *logic analyzer signal processor* CMOS gate array. However, the techniques for storing and plotting timing analyzer traces are radically different from oscilloscope traces. More specifically, on the faster time base settings, oscilloscopes use a technique known as *equivalent time sampling* to build up a display record over multiple triggers, resulting in an effective sample period of 50 ps or less (2.5 ps for the HP 54645A). Timing analyzer traces, however, are always single-shot—an entire waveform is reconstructed from each and every trigger, with an effective sample period exactly equal to the actual sample period. We therefore chose to double the maximum sample rate on the logic channels to 400 MSa/s to provide better single-shot time resolution. Using the same 50-MHz 16-bit VRAM memory as the HP 54645A, the HP 54645D has a total memory capacity of two million samples for each of eight digital channels (sampled at 400 MSa/s) or 1 million samples across all 16 digital channels (sampled at 200 MSa/s).

# Use of Deep Memory

It has long been recognized that one of the factors slowing the acceptance of the digital storage oscilloscope over the traditional analog oscilloscope has been the superior update rate of the analog oscilloscope. Update rate describes the number of waveforms that the instrument can display per unit time. Since update rate is representative of the percentage of the input waveform that actually gets displayed on the screen, it translates to the amount of information relayed to the user. In the past, digital storage oscilloscope manufacturers used a single-processor architecture to handle all user interface, acquisition, and display tasks. This has resulted in digital storage oscilloscopes gaining a reputation for having far inferior update rate capability compared to analog oscilloscopes.

One of the advantages that digital oscilloscopes hold over analog oscilloscopes is their ability to store the data for closer examination after the acquisition is stopped. Digital oscilloscopes with deep memory have been gaining popularity because of their ability to store a given amount of time with more timing resolution than oscilloscopes with less memory. The deeper an oscilloscope's acquisition memory, the more samples per unit time it can capture. To make full use of the deep memory, digital oscilloscopes provide the capability of *panning* (moving the display window earlier or later in time) and *zooming* (changing the display window to display more or less time). This allows the user to display the portion of the acquisition that is of interest, with the desired amount of detail.

Unfortunately, the update rate of the oscilloscope normally suffers with deep-memory acquisition architectures. The update rate is inversely proportional to the amount of memory captured. Since every data point processed has to be read out of an ADC converter and placed in capture memory by the acquisition system, more points translates to more time to process those points. The deep-memory digital storage oscilloscopes on the market before the HP 54645A/D always place the update rate/memory depth trade-off in the hands of the user by means of a human interface control for the acquisition memory depth. If the user is interested in panning and zooming the acquired data after stopping the acquisition, the memory depth can be increased to gain more timing resolution for this task. If the user is only interested in viewing repeated acquisitions of the signal, the memory depth can be decreased to improve the update rate. This requires that the user have an understanding of the trade-offs involved and a knowledge of the user interface so that the changes can be made.

The HP 54645A/D oscilloscope architecture is designed to optimize the memory depth for the user's requirements. If the user is viewing repeated acquisitions of the signal, the memory depth is decreased if necessary to maintain the maximum update rate. If the user stops the acquisition, the memory depth of the last acquisition is changed to use all of the available acquisition memory. This feature is made possible by the same architectural feature that was designed to maximize the oscilloscope's update rate. During most continuously acquiring configurations, half of the acquisition memory is used to write newly acquired data while the other half is being read into the display. Since the architecture is fundamentally based on a 1-million-point memory system, 500,000 points are dedicated to the next trigger while 500,000 points are being read to the display.

If memory depth has been traded off for update rate, a subset of 500,000 points is used for each trigger during continuous acquisition mode. For example, at 200  $\mu$ s/div, the acquisition time required to fill the screen with an acquired waveform is 200  $\mu$ s/div × 10 divisions = 2 ms. The time required to acquire 500,000 points at 200 MSa/s is the sample period times the number of points, or  $5.0 \times 10^{-9} \times 500,000 = 2.5$  ms. Since the time required to capture 500,000 points is larger than the time required to fill the screen, we choose to reduce the number of acquired points to maintain maximum update rate. In this case, 400,000 points can be acquired in 2 ms (400,000 ×  $5.0 \times 10^{-9} = 2$  ms), so we acquire 400,000 points. This maintains the theoretical update limitation of 500 waveforms per second (1/0.002 = 500). A more extreme trade-off occurs at 5  $\mu$ s/div. Only 10,000 points can be captured in the 50- $\mu$ s acquisition time (10,000 ×  $5.0 \times 10^{-9} = 50.0 \times 10^{-9}$ ).

If the user presses the Run/Stop key while an acquisition is in progress, the assumption is made that this may have been done to examine the last acquisition in more detail. The last acquisition that occurred before the user's action is stored in one half of the memory system. Since it cannot be assumed that more triggers will follow the user's action, this half of the memory may not be written to any more after the Run/Stop key is pressed. However, since the other half of the memory system now contains defunct data, the acquisition system is reconfigured to use the entire 500,000 points available in this other memory half, and keeps acquiring data, looking for a trigger. Since the primary task to be executed when the user presses the Run/Stop

key is to stop acquisition in what appears to be an instantaneous fashion, the system cannot wait forever for an additional trigger. Therefore, a timeout is initiated that will cause the system to cease looking for additional triggers after 100 ms. For the oscilloscope's acquisition system, this is a large window of opportunity to capture a deep-memory record. However, if no additional triggers occur, the acquisition system is brought to a stopped state, and the shorter acquisition obtained on the last trigger is used for postacquisition pan and zoom. Since most applications involve relatively frequently occurring triggers, this methodology will result in most users viewing deep-memory acquisitions every time they stop their oscilloscopes. For applications in which the rate at which triggers occur is uncertain, or in which there is only one trigger event, the user can press the Single key and guarantee a 1-million-sample acquisition for every trigger.

#### **The Decimation Problem**

Even with a million points of sample memory, at the slower time base settings, there will still be more samples across the screen than can be stored. We need to prune (*decimate*) the available data down to the memory size, then further thin the stored data down into 4000-point records for rapid display. In these situations, when the ADCs are sampling faster than the data can be used, the oscilloscope is said to be *oversampling*.

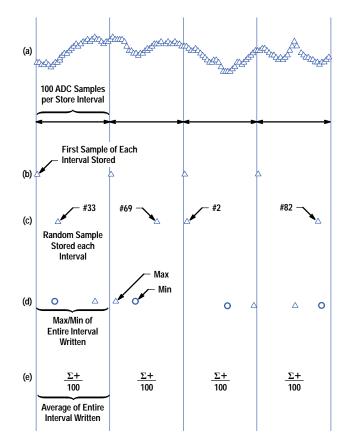

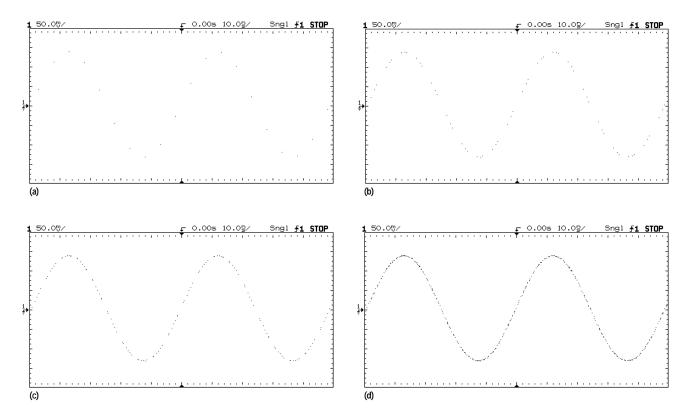

There are a variety of techniques available to perform this decimation process, each portraying a different representation of the input signal. Some methods will tend to highlight the subtle variations in the signal, others show the signal extremes, and others hide the signal extremes. As an example, suppose that the sample rate of the ADC is a factor of 100 greater than the desired store rate. Fig. 3 shows various decimation techniques for 100:1 oversampling.

*Fig. 3.* Various decimation techniques shown at 100:1 oversampling. (a) ADC samples. (b) Simple decimation. (c) Intra-acquisition dither. (d) Peak detection. (e) Smoothing.

Simple Decimation. One sample is stored and the next 99 ignored; then the next sample is stored and the next 99 ignored, and so on. This approach is illustrated in Fig. 3b. Since it is the simplest to implement, it is the most common decimation technique in digital oscilloscopes. Unfortunately, because of the very regular spacing of the stored samples, it is exceptionally prone to aliasing. Therefore, the HP 54645A/D rarely use this technique (only when calculating FFTs, when exact sample spacing is called for).

Intra-Acquisition Dithering. Rather than store the first sample during the sample interval, this patented technique stores a randomly selected sample for each interval. In Fig. 3c, sample #33 is stored during the first interval, then #69 during the second, then #2 in the third, and so on. This technique, used in all of the 546xx oscilloscopes, is remarkably effective against aliasing. The stored samples are not evenly spaced, so it becomes much more difficult for the sampled signal to "lock" to the samples. The HP 54645A/D oscilloscopes use this technique with an improved folding pseudorandom number generator.

It is used whenever the instrument is in the normal display mode. For more information on this sampling technique, see *Article 5*.

Peak Detection. Another common data compression technique is to store the minimum and maximum values of all of the samples in the sample interval, as shown in Fig. 3d. Widely used in digital oscilloscopes, this technique is called *peak detection*. When this technique is in use, rare, infrequent excursions are never ignored (lost), as they might be in the preceding two methods. This approach, however, tends to over-emphasize noise on the displayed record. Peaks are exaggerated and baselines become fatter at the expense of signal details. For example, an AM signal, peak detected, would show the modulation envelope quite clearly, but would lose the shape of the carrier wave. Statistical information about where the signal spends most of its time between the minimum and maximum values is lost.

The HP 54645A/D oscilloscopes combine traditional peak detection with intra-acquisition dithering when the instrument is in peak detection mode. They simultaneously acquire and plot both sampled versions of the incoming signal. The peak detected version highlights the signal extremes (one minimum/maximum pair per pixel column), while the denser conventionally sampled record (six points per pixel column) provides statistical information about the signal.

Smoothing. Yet another approach for decimating the incoming samples is shown in Fig. 3e. Here, rather than store the signal extremes for each interval, the average value is stored. This is logically equivalent to a simple low-pass boxcar filter cascaded with a decimating filter. At the slowest sweep speeds, millions of samples are averaged together for every point drawn on the screen, even on single traces. This display mode is useful for pulling the signal out of the noise.

While smoothing reduces the noise in the signal in a manner similar to conventional averaging, there are some differences. Smoothing works on signals acquired with a single trigger, while averaging requires multiple acquisitions to be effective. Smoothing functions as a low-pass filter with the cutoff frequency depending on the time base setting of the oscilloscope. When possible, the HP 54645A/D oscilloscopes use smoothing decimation when conventional averaging is turned on to provide additional noise reduction.

Logic Channel Decimation (Glitch Detection). The acquisition system of the HP 54645D mixed-signal oscilloscope has 16 logic channels. Decimating the series of 1s and 0s for these logic channels provides its own challenges. Simple decimation techniques would lose narrow glitches, so a peak detection technique (known as *glitch detection* in the logic analyzer domain) is always used. Two bits are sufficient to encode any sample interval, one value for each state (high and low). Not suffering from the drawbacks of peak detection on oscilloscope traces, logic waveforms are always acquired and plotted using glitch detection encoding regardless of the display mode selected for the oscilloscope channels.

#### **Trigger System Features**

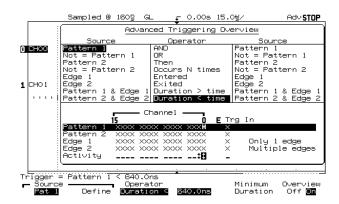

Perhaps the most difficult task of the design was the trigger architecture for the mixed-signal oscilloscope. It needed to be a mixture of both analog and digital trigger systems. The traditional oscilloscope triggering modes (rising or falling edges on any channel, with a variety of coupling and noise-reject selections) needed to be coupled with the logic triggering modes (pattern triggering, sequencing, Boolean AND/OR, and so on). But more significant, all of the cross-domain triggering circuits needed to be defined and developed.

Development of this cross-domain triggering system architecture and choices about which trigger modes to support were guided by two key design objectives. The first of these was to seamlessly integrate the trigger configuration for all channels, whether analog or digital. This allows any channel to be used as a trigger source in any trigger setup. A second objective was to extend this seamless trigger configuration to a full set of trigger features. This feature set extends far beyond traditional single-channel, edge-mode triggering to include functionality essential in a mixed-signal test environment.

In mixed-signal testing, digital signals are often grouped together to form a common data or address word. Consequently, pattern triggering using terms including all channels was an obvious need. Inclusion of analog channels in patterns also provides the unique capability to gate a digital address trigger specification with analog-level conditions. Use of a pattern-qualified edge term (pattern AND edge) is a second key capability, since it allows a typical read or write to be captured by specifying the address in the pattern specification and the edge as the read or write strobe. Specification of trigger sequences in the mixed-signal oscilloscope is a further capability that is especially useful in capturing cause-and-effect relationships between analog and digital signals. Finally, pattern duration and Boolean combinations of trigger terms are included.

# **Trigger Types**

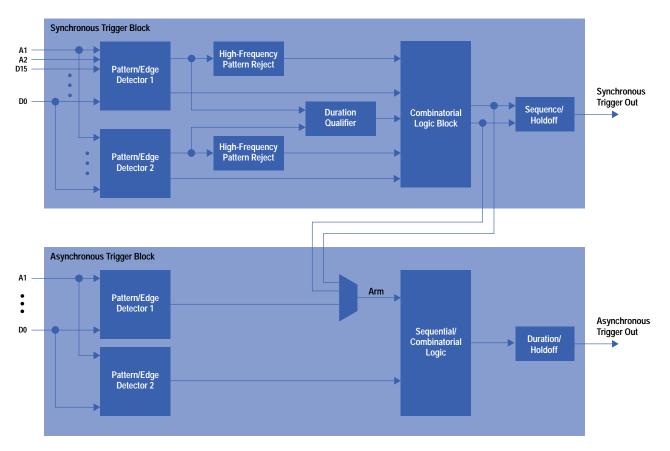

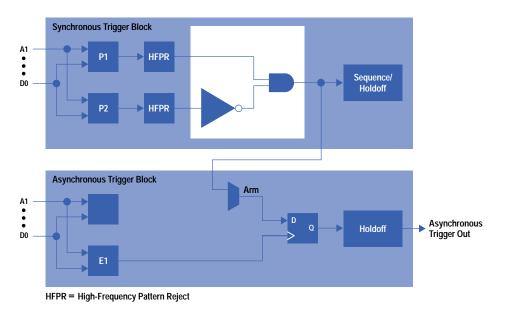

Design of a cross-domain trigger system to meet these objectives was influenced by trigger methods specific to timing analyzers and digital oscilloscopes. Typically, timing (and logic) analyzers triggering on pattern or complex logical terms assume that all trigger events are simultaneous with clock transitions (in our case the ADC sample clock). This is referred to as *synchronous trigger generation*. In the analog world of the oscilloscope, all trigger events are assumed to be asynchronous to clock edges. Since each of these methods has advantages, the final implementation of the HP 54645D trigger hardware uses two independent trigger systems, one for synchronous and one for asynchronous triggering.

Trigger features typical of timing analyzer capability include pattern triggering, sequences of pattern terms, pattern duration, and logical combinations of pattern and edge terms. In a timing analyzer, digital channels are normally grouped together and

trigger conditions are evaluated only at sample clock intervals. There are several advantages to this type of synchronous sample clock triggering. One is that trigger events are always visible on the display because events that occur between sample clocks cannot cause triggers. Also, the signal transition causing the trigger event to occur will not display any jitter at the trigger time because that time occurs at a sample clock edge. Furthermore, complex trigger sequences can be easily implemented in hardware using sequential logic. Finally, it is easy to reject spurious patterns by qualifying pattern detection over multiple samples.

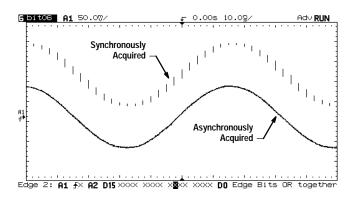

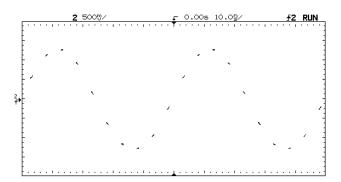

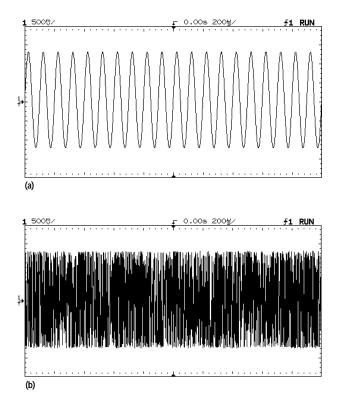

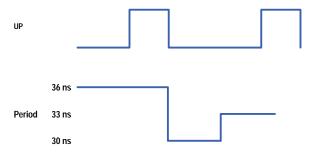

In a mixed-signal oscilloscope, triggering synchronously with the sample clock also has some significant drawbacks. Above all, it degrades equivalent time sampling operation for analog waveforms. This occurs because equivalent time sampling relies on random distribution of trigger events with respect to the sample clock and uses multiple triggered waveforms to enhance the analog display quality. The analog waveform display, when synchronously triggered at fast time base speeds, appears as a broken trace, with bunching of the signal at sample clock intervals (see Fig. 4). Since the HP 54645D samples at 200 MSa/s, degradation of waveforms is only severe at time base speeds of 20 ns/div or less. Furthermore, single-shot trigger captures are unaffected by synchronous triggering of the waveform.

Fig. 4. Effect of synchronous triggering on the waveform display.

A second drawback of synchronous triggering is that if the sample rate is too low, trigger events can be totally missed. This is not a problem in the HP 54645D mixed-signal oscilloscope because the sampling interval (5 ns) is smaller than the minimum width of any pulse passed by the 100-MHz analog bandwidth ( $\sim$ 7 ns).

Asynchronous trigger generation, traditional in digital oscilloscopes, provides precise trigger timing information to the waveform display. This allows the use of equivalent time waveform reconstruction to combine multiple trigger events and optimize signal display for repetitive signals at fast time base speeds. In addition, trigger time resolution for single-shot captures is limited only by analog channel bandwidth, rather than by sample time granularity. However, asynchronous trigger generation does have one significant drawback. It is possible that the event that generates the trigger may not be visible in the waveform display. This possibility exists because an analog event may cross a trigger threshold and then fall below the threshold again between successive sample clocks. In the HP 54645D, this effect is minimized because the analog bandwidth of the trigger path limits detectable input pulse widths to about 7 ns (depending on threshold level) while the minimum sampling interval is 5 ns.

# Mixed-Signal Oscilloscope Trigger System Architecture

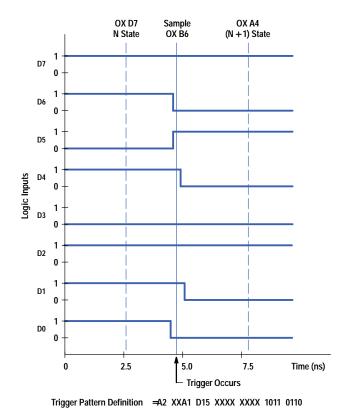

To achieve optimal signal display quality and maximize trigger capabilities, the HP 54645D mixed-signal oscilloscope uses both synchronous and asynchronous triggering. The hardware architecture, shown in Fig. 5, includes dual trigger paths that implement this trigger capability. The synchronous trigger path includes a full set of pattern and edge detectors, which allow independent detection of all trigger terms. A pattern duration block is also included to allow triggers based on pattern duration less than target time, greater than target time, and in a target time range. An important feature of this path is the inclusion of high-frequency pattern rejection blocks. These blocks require that patterns be present for a fixed number of sample periods. This enables rejection of patterns that are only present at bus transitions because of channel-to-channel skew. An example of this skew in shown in Fig. 6, where a transition is made between address values of D7 and A4 (hexadecimal). Since the sample clock is not synchronized with the address transition, the sample clock will occasionally occur during transition states (in this case the address B6) and trigger on these patterns unexpectedly. With the high-frequency reject enabled, these triggers are rejected because they are only present for very short times (typically less than 1 ns). The pattern rejection block is automatically programmed by the CPU to require a minimum of two samples for all pattern definitions with more than one defined level. Outputs from the trigger terms detected are then routed through combinatorial logic blocks, sequencing, and holdoff. The design of this path allows for a completely orthogonal set of trigger logic terms.

The asynchronous trigger path provides similar trigger functionality, including edge trigger, pattern detection, pattern-qualified edge detection, pattern duration, and Boolean logic combinations of trigger terms. Since this path lacks

Fig. 5. HP 54645D trigger system block diagram.

Fig. 6. Triggering on a channel-to-channel skew state (B6 hexadecimal).

multiple edge detection blocks, only single-edge trigger terms can be configured. Also, only one pattern-qualified edge detection can be configured. The ability to do cross-domain triggering with synchronously configured pattern terms arming the asynchronous trigger path significantly broadens the configuration choices. For example, an advanced pattern definition of (P1 AND E1) AND (NOT = P2) can be implemented by synchronously detecting P1 AND (NOT = P2) and using this to arm the asynchronous block, which then detects E1 (see Fig. 7).

Fig. 7. Cross-domain trigger configuration.

Based on the current trigger term definitions and channel display selections, the mixed-signal oscilloscope CPU configures either the synchronous or the asynchronous trigger path as the trigger source for the instrument. To optimize the analog channel display quality, triggers are set up asynchronously, if possible, for all cases in which analog channels are on or analog edges are used in trigger terms. This context-sensitive implementation allows the use of equivalent time sampling to enhance analog waveform display in all possible cases. Consequently, waveform display is optimized without the need for the user to know the details of the trigger configuration.

# Mixed-Signal Oscilloscope Trigger Applications

Typical trigger applications for the HP 54645D mixed-signal oscilloscope use the rich set of triggering functions to capture events combining analog and digital criteria. The following paragraphs present specific examples that show the unique capabilities of the mixed-signal oscilloscope trigger system.

ADC Performance Evaluation. Dynamic ADC performance can be evaluated using either pattern triggering to trigger on specific digital outputs or edge triggering with the analog threshold set to the level of interest. By providing an input sawtooth waveform, slew rate effects, missing codes, and nonlinearities can easily be evaluated.

Gated Processor Address Read/Write. An edge-qualified pattern detection can be used to detect a processor read or write to a specific address. By using analog channels in the pattern definition, it is possible to gate the trigger so that only processor reads and writes are displayed that occur when an analog signal is in a specific state. For example, in an alarm system in which a processor normally polls critical sensors to determine if alarm conditions exist, the use of a gated pattern and edge trigger could allow a display of all processor activity starting with (triggering on) the first processor read for which the sensor state indicates an alarm.

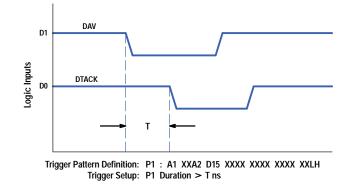

Glitch/Pattern Duration. Glitch triggering allows triggering on the duration between the positive and negative edges of a single signal. This allows capture of pulses less than a specific pulse width (glitches), greater than a specific pulse width, and within a specific pulse width range. This is very useful for capturing events that are in or out of specific timing requirements. Pattern duration allows the same duration-triggering choices but combines up to eighteen channels in the pattern definition so that triggering on the timing of combined channels is obtained. A specific example of using pattern duration is in capturing timing violations for a data handshake (see Fig. 8). The time for data acknowledgment after data valid must be less than a maximum time T. Violation of this timing could be found by setting pattern terms DAV low and DTACK high and looking for pattern duration greater than T.

Fig. 8. Pattern duration triggering to find a timing violation.

**Interrupt Response/Latency**. Using a trigger sequence such as E1 THEN P1 AND E2 allows triggering on a processor response to an interrupt by first triggering on a hardware interrupt to a processor and then on a write to a register that is the ultimate response of the processor to the interrupt. The value written out can be read and subsequent events can be traced. Since the mixed-signal oscilloscope captures negative-time (pretrigger) events, this trigger can also be used to measure interrupt processing latency.

Register Write/Analog Response. In control applications, it is useful to be able to trigger on an analog signal that is controlled by the setting of a control register. This can also be achieved by a trigger sequence such as pattern AND edge THEN edge. For example in a motor control application, this trigger sequence can be used to trigger on a write to a control register followed by a motor commutation.

#### **Display Enhancements**

In the HP 546xx family of products, waveform update and display have always been high priorities in the design. Traditionally, digital oscilloscopes have had a slow update rate of data to the screen. In the HP 54645A/D the update rate has been increased to approximately three million points per second. This gives a much closer representation of the way an analog oscilloscope displays waveforms. For instance, on an amplitude modulated signal, an analog display would show the upper and lower boundaries with a filled-in area between them. On a traditional digital oscilloscope you would only see a few waveforms inside those boundaries. However, because of the increased update rate on the HP 546xx family, you see the boundaries and the area inside filled with data, a display that matches the traditional analog oscilloscope much more closely. This helps by displaying waveforms more closely to their true nature, but by itself does not address other features of an analog display such as its inherent intensity variation as a function of slew rate.

Analog oscilloscopes generally use a cathode-ray tube (CRT) in which an electron beam is swept across a display at a fixed speed while being deflected in the vertical direction by an analog signal. Because of this, areas of the waveform that have a high slew rate, such as edges, are displayed at a lower intensity than areas such as the top of a waveform, where the slew rate is low. This intensity variation provides information to the user that is not available with a traditional digital oscilloscope. For example, square waves displayed on an analog display are brighter at the top and bottom where the slew rate is low, and quickly changing edges are at a much lower intensity. For another example, consider a waveform that has a lot of baseline noise. On an analog display, the persistence of the phosphor causes the baseline to be very bright and infrequent noise to be dim. On a digital display, the noise is accentuated because all of the data points are displayed with the same relative intensity. This presents the digital oscilloscope designer using a raster display with a real challenge. How to display the waveforms to give a more accurate representation of their time-varying nature?

One thing to note is that the analog oscilloscope doesn't display infrequent signals very well. Because the phosphor has a limited persistence, the waveform will fade after a short time and if not redrawn will not be visible. One attempt to solve this problem is the analog storage oscilloscope, which uses a special plate in the CRT that has a much longer persistence. This is not a perfect solution because the waveform tends to bloom on this type of display and will still fade over time. It is also fairly expensive. A solution in the digital realm has been to use color, displaying data points that are sampled frequently in a bright color that is dimmed at a computed fade rate to simulate a long-persistence phosphor. However, color displays are more expensive, and more memory is needed to keep the counts for each data point. This can also be done with a monochrome display by varying the brightness of a data point in time, but more memory is still required, and in both cases an increased computational burden is placed on the display software. None of these methods addresses the problem of displaying different slew rates at different intensities.

The HP 54645A/D oscilloscopes use a proprietary variable-intensity algorithm to control the intensity of each data point. Adjacent points in the same raster row are used to set the intensity of the current point. Therefore, a point with horizontal neighbors will be brighter than if it has none. In the HP 54645A/D oscilloscopes, two intensity levels are used: full-bright and half-bright. When a point has a neighbor on both sides it is displayed full-bright. When it has zero or one neighbor, it is displayed half-bright. Thus, a high-slew-rate edge is displayed with less intensity because it has no horizontal neighbors.

Looking again at the square wave, the edges will be displayed at a lower intensity than the top and bottom of the signal, which results in a display that looks much more like the analog oscilloscope's representation of the waveform. For the signal with a noisy baseline, the noise away from the baseline is displayed at a lower intensity because the data points do not have horizontal neighbors. The cost to implement this enhancement is greatly reduced because inexpensive printed circuit board hardware is used. The update rate of the waveforms is not affected because this method can be used on the fly as data points are being displayed.

One other enhancement is used when the HP 54645D displays logic waveforms. These traditionally have a high value and a low value with edges drawn between them when the waveform changes. On a raster display, we have a fixed horizontal resolution in which to place the data points. The display is divided into rows and columns of addressable points called pixels. Suppose a point falls at the boundary between two horizontal pixels. On some acquisitions it will be displayed in one pixel, on others in the adjacent pixel. This results in a double-wide full-bright edge. Compared with a point that falls in the middle of a pixel, it will seem brighter. On a display with many logic waveforms this adds a perceptible flicker. The HP 54645D solves this by displaying double-wide pixels half-bright and single-wide pixels full-bright. This has the effect of equalizing the intensity and greatly reducing the perceived flicker.

In all of these methods an attempt was made to give the HP 54645A/D oscilloscopes a display that does its best to represent the waveforms the user might encounter.

#### Acknowledgments

We would like to acknowledge the technical contributions of Mike Beyers, Stu Hall, Dana Johnson, Pat Burkart, Warren Tustin, Derek Toeppen, Ken Gee, Frank Leri, Marty Grove, and Dan Timm. Jerry Murphy led the marketing effort. Bob Witte and Steve Warntjes managed the whole affair.

#### Reference

<sup>1.</sup> R.A. Witte, "Low-Cost, 100-MHz Digitizing Oscilloscopes," *Hewlett-Packard Journal*, Vol. 43, no. 1, February 1992, pp. 6-11.

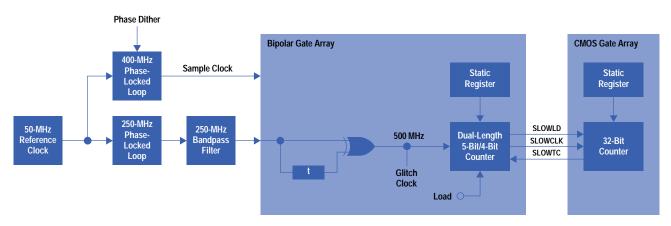

# A Cost-Effective Architecture for a 500-MHz Counter for Glitch Trigger

The HP 54645A and 54645D oscilloscopes can trigger on pulses qualified by their width, a feature known as *glitch trigger*. The time qualification is done with a 500-MHz, 37-bit counter that provides 2-ns timing resolution over an 8-ns-to-100-s range. Operation at 500 MHz (a 2-ns period) is too fast for CMOS logic, but the 37-bit counter is too large for economical integration in bipolar logic. The clock for the counter must be asynchronous with the analog-to-digital sampling clock so that the time at which a trigger is generated is in no way related to the times of the samples. Otherwise, in random repetitive acquisition mode (also known as equivalent time sampling), the samples would not be randomly distributed with respect to the input signal and the oscilloscope waveform would contain missing segments.

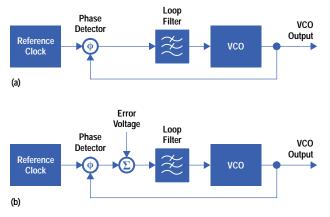

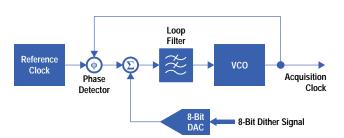

The block diagram in Fig. 1 shows how these requirements and constraints were satisfied. The least expensive way to obtain the 500-MHz glitch trigger clock was with a commercial single-chip phase-locked loop locked to the 50-MHz reference clock. The phase-locked loop synthesizes a 250-MHz clock, which is doubled to 500 MHz in the bipolar gate array. Phase locking to the reference clock guarantees that the glitch trigger clock is precisely synchronized with the reference. Since the sample clock is also locked to the reference but phase dithered, the glitch and sample clocks have random phase with respect to each other, preventing missing segments in the waveform.

Fig. 1. Block diagram of the 500-MHz, 37-bit counter.

The clock doubler generates an active 500-MHz edge on both the rising and falling edges of the 250-MHz clock. The symmetry of the 250-MHz clock affects the uniformity of the periods of the 500-MHz clock. The jitter of the 250-MHz clock causes period jitter in the 500-MHz clock. The delay element  $\tau$ , formed with gate delays, determines the duty cycle of the 500-MHz clock. The asymmetry and period jitter errors of the 500-MHz clock must both be less than 100 ps to preserve timing margins in the 500-MHz counter. The phase-locked loop IC alone cannot meet these requirements, so a bandpass filter is introduced that removes spurious components in the clock spectrum, improving the symmetry and reducing the jitter from 111 ps to 44 ps.<sup>1</sup>

For reasons of both power and cost, the 37-bit counter is too large to implement entirely in the bipolar gate array. By including only a few of the low-order, high-speed bits in the bipolar IC and the remaining bits in a CMOS gate array we are able to build a very economical, low-power 500-MHz counter. The bipolar portion is called the fast counter and the CMOS portion the slow counter. Together these two operate as a single 37-bit synchronous counter.

The design of the counter is complicated because the CMOS IC must never see pulses narrower than about 10 ns and responds relatively slowly with the terminal count (TC) signal. To overcome these limitations the fast counter operates in either of two modes: as a five-bit counter or as a four-bit counter. For counts from 1 to 31 the fast counter performs all the counting. For counts of 32 and up, the bipolar counter is always loaded with a count between 15 and 31. Since the fast counter is loaded with a minimum count of 15, the slow counter always has at least 15 × 2 ns or 30 ns to reload itself before it is called upon to begin counting. The fast counter counts down in five-bit mode to zero and then generates a SLOWCLK signal, triggering a count in the slow counter. It then switches to 4-bit mode and counts down, generating a SLOWCLK signal every 15 clocks. Thus, the slow CMOS counter is clocked at only 500 MHz/15 or 33 MHz and has 30 ns in which to generate SLOWTC. These requirements are easily met with modern CMOS gate array technology.

Steven D. Roach Development Engineer Electronic Measurements Division

#### Reference

1. S.D. Roach, "Achieving Ultra-Low Clock Jitter with Commercial High-Speed Clock Generators," *Proceedings of Design Supercon '96*, High-Performance System Design Conference, Santa Clara, California, 1996.

# Sustained Sample Rate in Digital Oscilloscopes

At all but a few of the fastest sweep speeds, the acquisition memory depth and not the maximum sample rate determines the oscilloscope's actual sample rate. Peak detection capability, when used correctly, can make up for acquisition memory shortfalls.

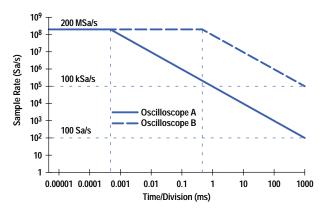

# by Steven B. Warntjes

One of the most basic specifications in digital oscilloscopes is the maximum sample rate. Oscilloscope users often understand the theory of signal sampling and signal reproduction, but often mistakenly assume that the oscilloscope always samples at its maximum sample rate. In reality, two specifications need to be considered: the maximum sample rate and the acquisition memory behind the signal sampler. At all but a few of the fastest sweep speeds, the acquisition memory depth and not the maximum sample rate determines the oscilloscope's actual sample rate and consequently how accurately the input signal is represented on the oscilloscope display. The deeper the acquisition memory, the longer the oscilloscope can sustain a high sampling frequency on slow time-per-division settings, thus increasing the actual sample rate of the oscilloscope and improving how the input signal looks on the oscilloscope screen.

The digital oscilloscope's peak detection specification is another often overlooked specification. This important feature, when used correctly, can make up for acquisition memory shortfalls. In addition, peak detection can be combined with deep acquisition memory to create unique advantages in digital oscilloscopes.

#### **Digital Oscilloscope Sampling**

Basic sampling theory states that for a signal to be faithfully reproduced in sampled form, the sample rate must be greater than twice the highest frequency present in the signal. This sample rate is known as the Nyquist rate.<sup>1</sup> For an oscilloscope, this means that if the user wants to capture a 100-MHz signal, the sample rate should be at least 200 MSa/s. While the theory states that greater than  $2 \times$  sampling is sufficient, the practicality is that to reproduce the input signal with  $2 \times$  sampling requires complex mathematical functions performed on many samples. *Reconstruction* is the term commonly given to the complex mathematical functions performed on the sampled data to interpolate points between the samples. In practice, oscilloscopes that do reconstruction typically have less than perfectly reproduced waveforms because of imperfect application of the mathematical theory,\* and they may have a slow waveform update rate because of the time it takes to do the necessary computations.

One solution to the reconstruction problem is to sample the waveform at a rate much higher then the Nyquist rate. In the limit as sampling becomes continuous, as it is in an analog oscilloscope, the waveform looks "right" and requires no reconstruction. Consequently, if the digital oscilloscope can sample fast enough, reconstruction is not necessary. In practice, a digital oscilloscope rule of thumb is that  $10 \times$  oversampling is probably sufficient not to require reconstruction. This rule dictates that a digital oscilloscope with 100 MHz of bandwidth would require an analog-to-digital converter (ADC) to sample the input signal at 1 GSa/s. In addition, the acquisition memory to hold the samples would have to accept a sample every nanosecond from the ADC. While memories and ADCs in this frequency range are available, they are typically expensive. To keep oscilloscope prices reasonable, oscilloscope manufacturers minimize the amount of fast memory in their oscilloscopes. This cost minimization has the side effect of dramatically lowering the real sample rate at all but a few of the fastest time-per-division settings.

The sampling theory presented above assumes that the sampler only gets one chance to "look" at the input signal. Another solution to the reconstruction problem is to use repetitive sampling. In repetitive sampling, the waveform is assumed to be periodic and a few samples are captured each time the oscilloscope sees the waveform. This allows the oscilloscope to use slower, less expensive memories and analog-to-digital converters while still maintaining very high effective sample rates across multiple oscilloscope acquisitions. The obvious disadvantage is that if the waveform is not truly repetitive the oscilloscope waveform may be inaccurately displayed.<sup>2</sup>

# **Digital Oscilloscope Memory Depth**

Now that we understand digital oscilloscope sampling requirements, we can examine how memory depth in oscilloscopes affects the sample rate at a given sweep speed or time-per-division setting. The time window within which a digital oscilloscope can capture a signal is the product of the sample period and the length of the acquisition memory. The

<sup>\*</sup> Errors are attributable to high-frequency components in the captured signal and a finite number of samples.

acquisition memory is measured by the number of analog-to-digital converter samples it can hold. Typically in digital oscilloscopes the length of the acquisition memory is fixed, so to capture a longer time window (adjust the oscilloscope for a slower time-per-division setting) the sample rate must be reduced:

$t_{CAPTURE} = k_{MEMORY}/f_s$ ,

where  $t_{CAPTURE}$  is the time window captured by the oscilloscope,  $k_{MEMORY}$  is the length of the acquisition memory, and  $f_s$  is the sample rate.

In Fig. 1 we have oscilloscope A with a maximum sample rate of 200 MSa/s and an acquisition memory depth of 1K samples. Oscilloscope A samples at its maximum sample rate specification of 200 MSa/s or 5 nanoseconds per sample from 5 ns/div to 500 ns/div. As the time-per-division increases beyond 500 ns/div we see that the sample rate drops. At 1 millisecond per division the oscilloscope's sample rate has dropped to 10  $\mu$ s per sample or 100 kSa/s. This dramatic drop in sample rate at slower sweep speeds leads to oscilloscope displays of fast signals that don't accurately represent the input signal.

*Fig. 1.* Effect of memory depth on the maximum sample rate of a digital oscilloscope. Oscilloscope A has a memory depth of 1000 samples. Oscilloscope B has a 1,000,000-sample memory.

Fig. 1 also shows the sample rate behavior of oscilloscope B, which differs from oscilloscope A only in that the memory depth has been increased from 1,000 samples to 1,000,000 samples. Oscilloscope B samples at its maximum sample rate of 200 MSa/s from 5 ns/div to 500  $\mu$ s/div. On fast time base settings, oscilloscopes A and B both sample at 200 MSa/s. An important difference shows up at the slower time base settings. At 1 millisecond per division we see that oscilloscope B samples at 100 MSa/s or 10 nanoseconds per sample while oscilloscope A has dropped to 100 kSa/s. We can clearly see that the deeper memory (×1000) gives us the ability to capture events 1000 times faster at the slower time-per-division settings. The effect of deeper memory is the ability to sustain the maximum sample rate at much slower sweep speeds, in our example from 500 ns/div to 500  $\mu$ s/div, and sustain faster sample rates at sweep speeds where the sample rate must be reduced because of memory depth limitations. This effect of increased acquisition memory gives the oscilloscope higher sampling performance over a wider range of oscilloscope operation.

# **Digital Oscilloscope Peak Detection**

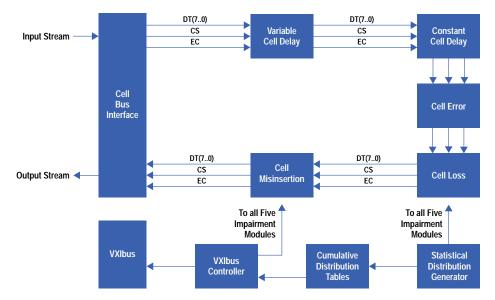

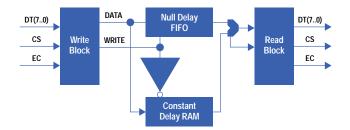

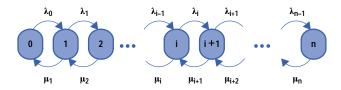

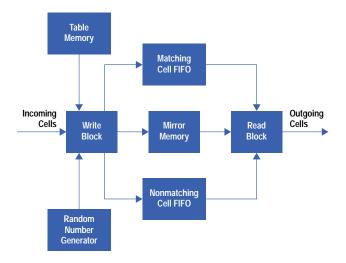

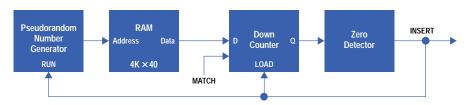

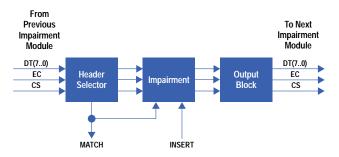

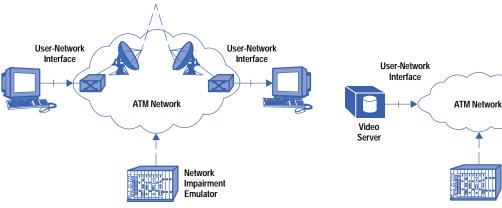

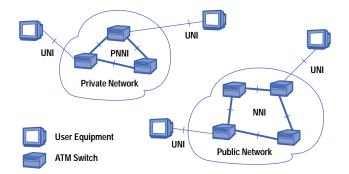

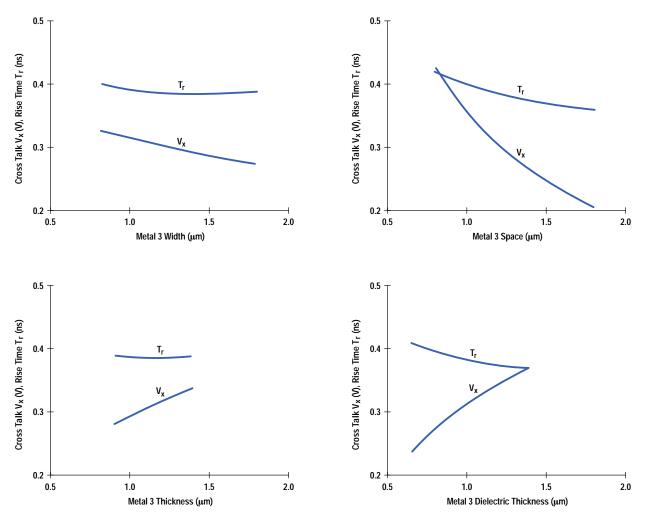

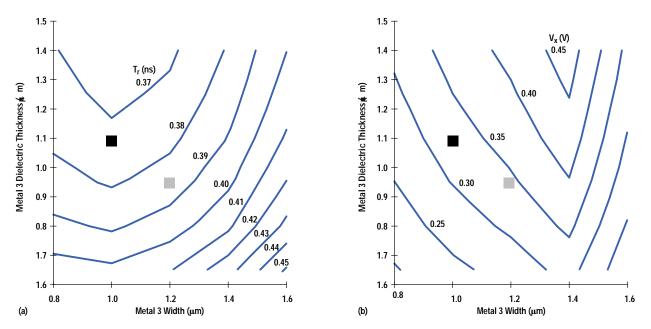

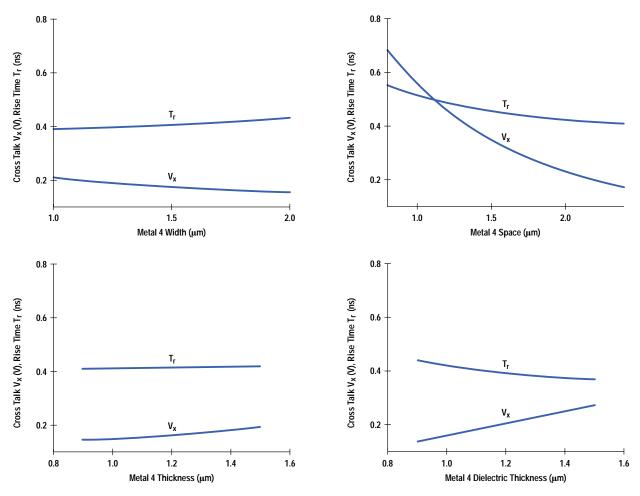

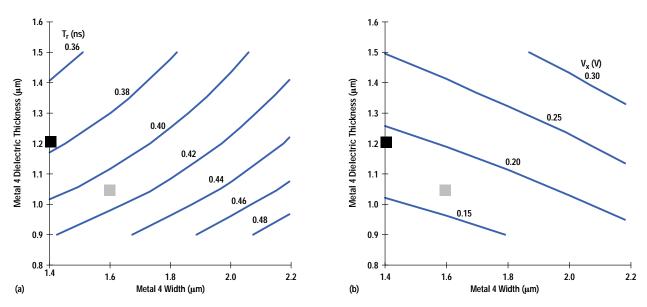

Peak detection is a powerful feature that compensates for lack of memory depth in digital oscilloscopes. In peak detection mode the oscilloscope looks at many samples but stores only the maximum and minimum voltage levels for a given number of samples. The effective sample rate of the oscilloscope in peak detection is normally the maximum sample rate of the oscilloscope on all sweep speeds.\* This enables the oscilloscope to capture fast input signal amplitude variations by sampling at the maximum sample rate, yet save memory space by storing only the significant signal deviations. The value of peak detection is best illustrated with a simple example. In Fig. 2 we have a display of a long time window with short-duration changes in signal amplitude. We are at a time-per-division setting of 20 seconds per division and are showing a 100-nanosecond event. To detect this event without peak detection would require at least a 1/(100 ns) = 10-MSa/s sample rate. Likewise, to capture 200 seconds (20 s/div  $\times$  10 div) of information with 100-ns sampling would require a memory depth of 200/(100 ns) or two billion samples. Clearly, peak detection is useful for catching short-duration signal changes over long periods of time without large amounts of oscilloscope acquisition memory. In many instances peak detection can make up for acquisition memory shortfalls.